Innovative Solutions

PETsys Electronics develops cutting-edge microelectronics ASICs and complete readout systems for fast photosensors. Our technology serves diverse applications including PET medical imaging, physics experiments, LiDAR, security, geo-tomography, and more.

Our integrated approach combines proprietary electronics with LYSO crystals and silicon photosensors to deliver substantial improvements in PET system performance.

Scalability Through Integration: Our SiPM-based gamma-ray detectors use dedicated, highly integrated ASICs designed for low noise and low power consumption. This integration is essential for scaling systems to tens of thousands of channels while maintaining consistent performance across the entire array.

Exceptional Timing Performance: PETsys SiPM modules achieve coincidence time resolution (CTR) of approximately 200 ps FWHM. This excellent timing enables Time-of-Flight (ToF) PET imaging, producing sharper, cleaner images with reduced noise and improved diagnostic quality.

High Spatial Resolution: Our highly pixelated PET detector modules deliver approximately 1 mm spatial resolution using either one-to-one crystal coupling or light-sharing configurations. Double-readout modules achieve industry-leading depth-of-interaction (DoI) resolution of approximately 3 mm in complete scanner systems.

Cost-Effective & Flexible Design: The high level of integration in PETsys electronics ensures low cost per channel, compact system footprint, and minimal power consumption. Our front-end modules are engineered for straightforward integration into whole-body PET scanners and adapt to specialized geometries. While detector modules may require customization for specific applications, the core electronics architecture remains consistent across different configurations, reducing development time and cost.

Our Product Porfolio Includes:

ASICs for reading and digitizing fast light signals from SiPMs, MCPs, and other modern photosensors

High-performance analog components: amplifiers, discriminators, charge integrators, DACs, ADCs, and TDC

Front-end electronics boards that interface directly with photosensors and detectors

Data acquisition and system-control electronics featuring large FPGAs, fast optical links, and GbE/PCIe interfaces

Complete solutions encompassing hardware, firmware, and software for advanced detector readout into DAQ computer

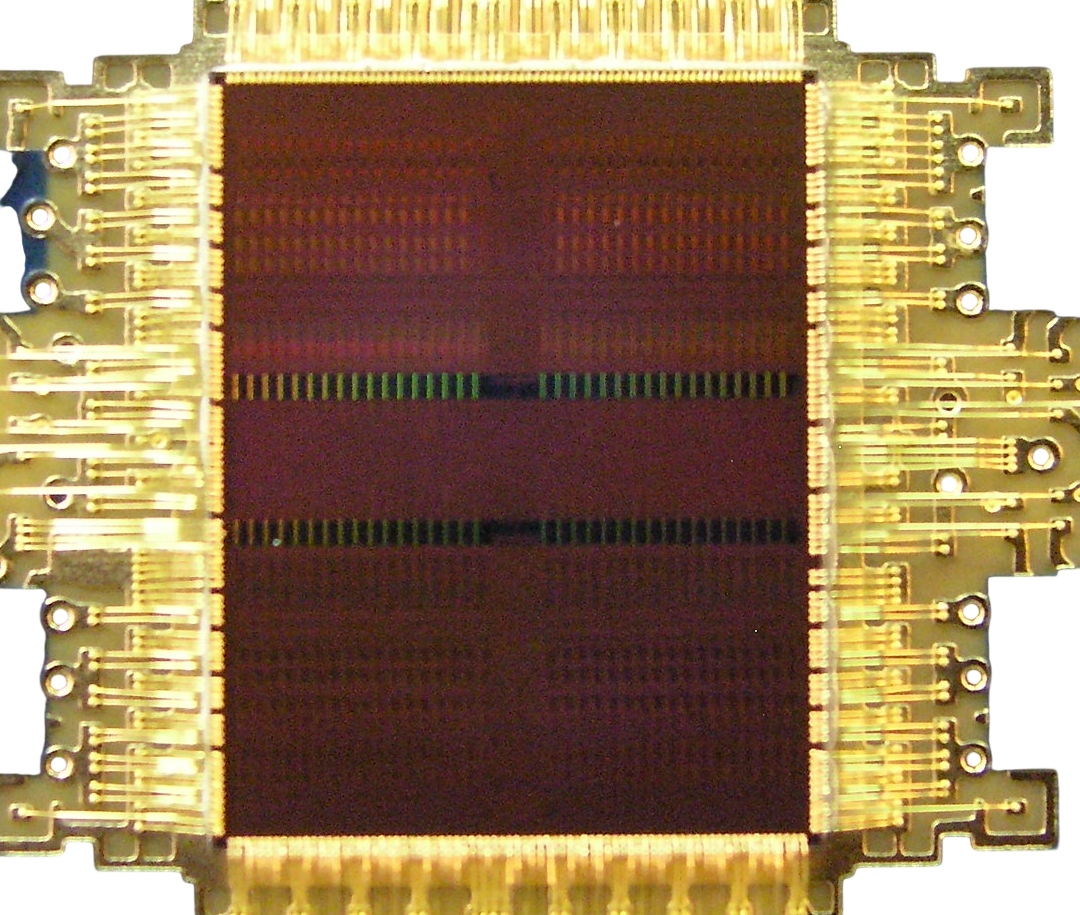

Advanced ASIC Technology

PETsys Electronics develops state-of-the-art, low-power mixed-signal ASICs that read and digitize fast signals from modern photosensors used in PET scanners and related applications.

Modern PET imaging requires electronics that can keep pace with rapid advances in scintillators and photosensors designed for ultra-fast timing. Our ASICs are engineered to have minimal impact on overall PET system performance while delivering high integration density and low power consumption—both critical requirements for large-scale imaging systems and Total-Body PET scanners.

Key Design Principles:

- High-precision signal processing that preserves photosensor timing and energy resolution, ensuring minimal impact on overall system performance

- High integration density enabling compact designs with tens of thousands of channels

- Low power consumption making large-scale systems practical and cost-effective

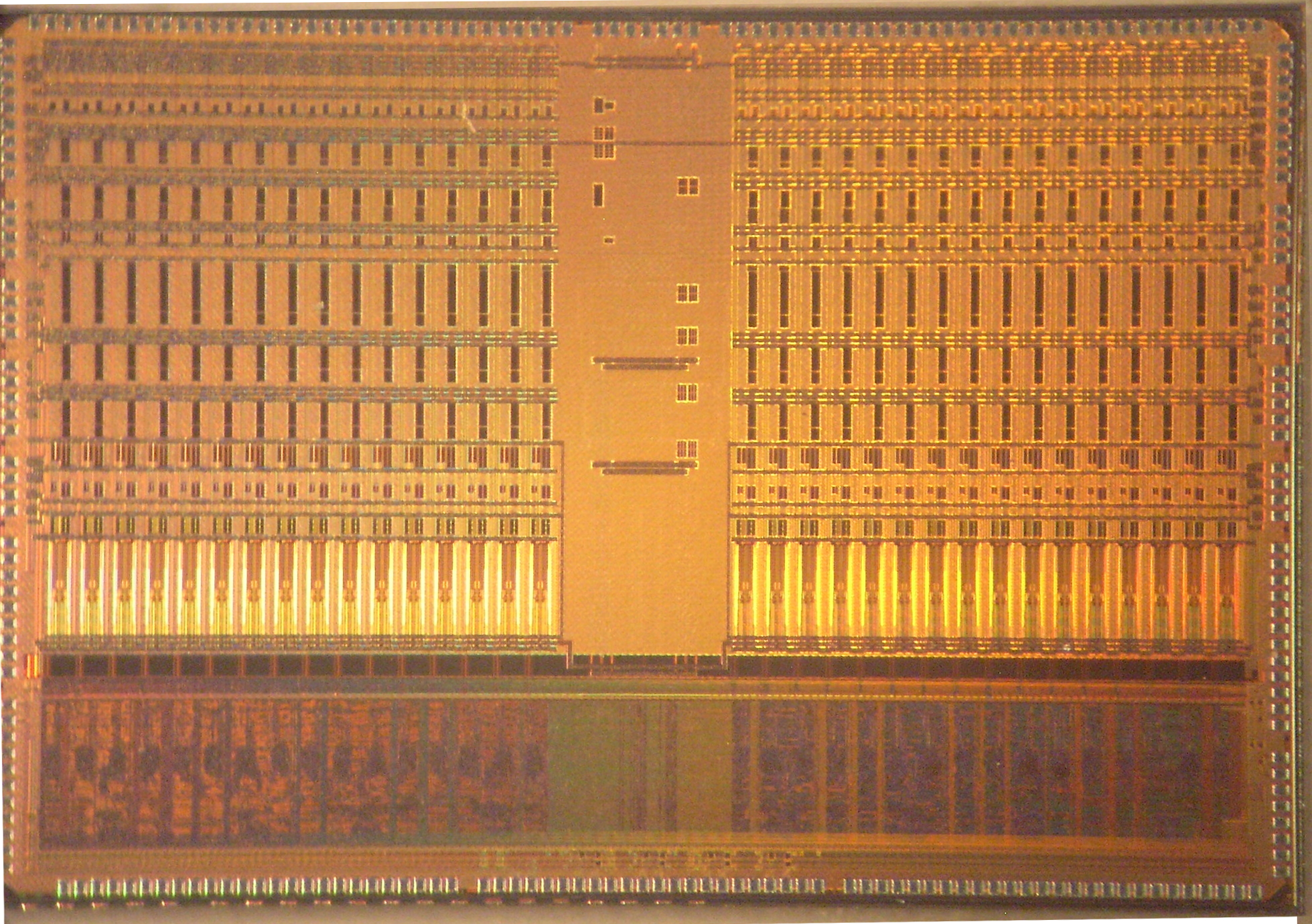

Since 2013, PETsys Electronics has been developing and improving the TOFPET family of ASICs

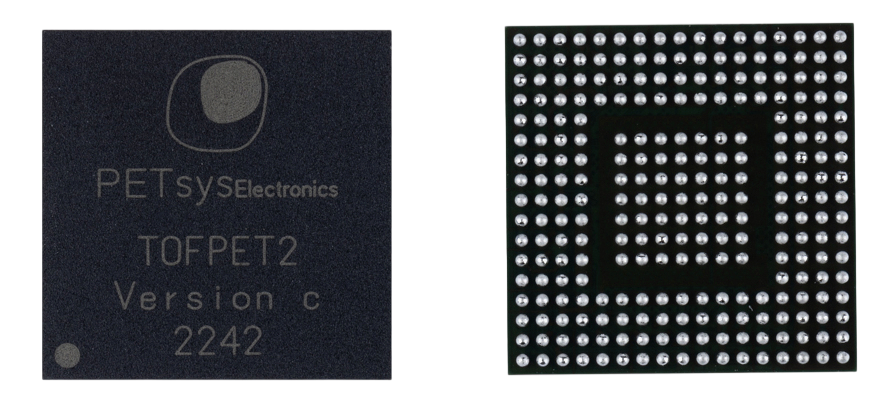

TOFPET2: Core Technology and Established Performance

Introduced in 2017, TOFPET2 ASIC has been the cornerstone of PETsys commercial success and remains the foundation of all current PETsys-based systems deployed worldwide.

TOFPET2 is a low-noise, low-power, 64-channel ASIC optimized for fast timing and high data-rate applications such as TOF-PET.

Key Features:

Dual thresholds per channel providing independent timing and event triggering

Low-impedance input amplifier using regulated common-gate topology

Quad-buffered analog interpolation TDCs with 30 ps time binning

Charge-integration ADCs and Time-over-Threshold (ToT) amplitude measurement

Maximum event rate of 480 kHz per channel

Dark-count rejection capability up to 2 MHz

TOFPET3: Next-Generation Development

PETsys is currently developing the next-generation TOFPET3, targeting improvements in timing resolution, energy linearity, and overall performance while maintaining low power consumption and high event-rate capability

The first prototype has demonstrated promising results, presented at IEEE NSS-MIC 2024:

CTR below 100 ps using LYSO crystals and AFBR-S4N22P014M SiPMs.

Single-photon triggering capability

Excellent energy measurement linearity and resolution

Development continues with planned improvements including enhanced timing circuits targeting approximately 25 ps ASIC-level CTR contribution, optimized energy measurement circuits with single-photon sensitivity (SNR > 10), four auxiliary channels with configurable analog summing (16/32/64 channels) for light-sharing applications, and advanced triggering features for selective channel readout.

SiPM Readout Systems

PETsys SiPM Readout Systems are engineered to manage large numbers of SiPM pixels in high-rate applications requiring excellent timing performance. Built around the TOFPET family of ASICs, these systems convert analog sensor signals to digital readout with exceptional precision and scalability.

The readout system uses four main component types to build complete data acquisition solutions:

System Architecture Principles

Front-End Modules (FEMs)

FEMs receive SiPM signals and house the TOFPET ASICs that perform the initial signal processing. Different FEM types vary in ASIC count, form factor, and geometry to accommodate diverse detector designs.

Each FEM outputs digital data corresponding to the time and amplitude of detected events via LVDS links. The modules receive system-wide timing and synchronization signals, power, and SiPM bias voltages through a main I/O connector. ASIC configuration is managed via an SPI interface.

Front-End Type D Boards (FEB/Ds)

FEB/D boards connect to multiple FEMs and serve as the data aggregation and processing hub. Depending on component selection, each FEB/D handles between 1,024 and 8,192 SiPM channels. The boards also differ in maximum DC-DC power delivery capacity. Their core functions are:

- Collect and frame events from connected FEMs

- Compute and apply trigger filters for event selection

- Transmit processed data to the computer interface

FEB/D boards accept two types of mezzanine cards:

- Comm-DAQ/GBE: Implement the output data links (high-speed optical/copper or Gigabit Ethernet)

- Bias-16P/32P: Provides 16 or 32 independent SiPM bias voltage channels

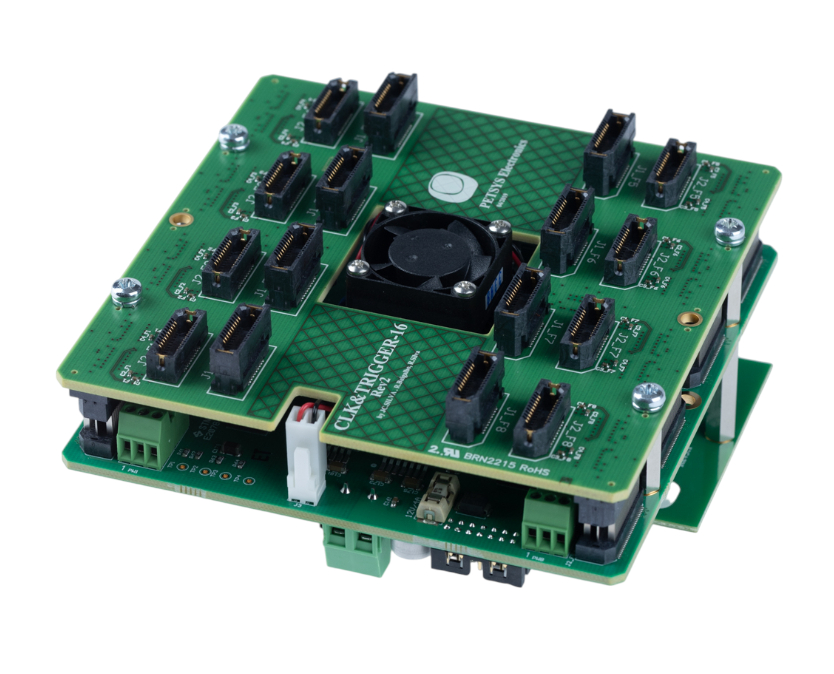

Clock & Triger Board (CLK&TGR)

The Clock & Trigger board ensures system-wide synchronization by distributing timing signals and coordinating coincidence triggers across 16 boards. It receives trigger bits from individual FEB/Ds and implements the coincidence logic essential for PET imaging. An enhanced version supporting up to 64 FEB/D modules is currently in development.

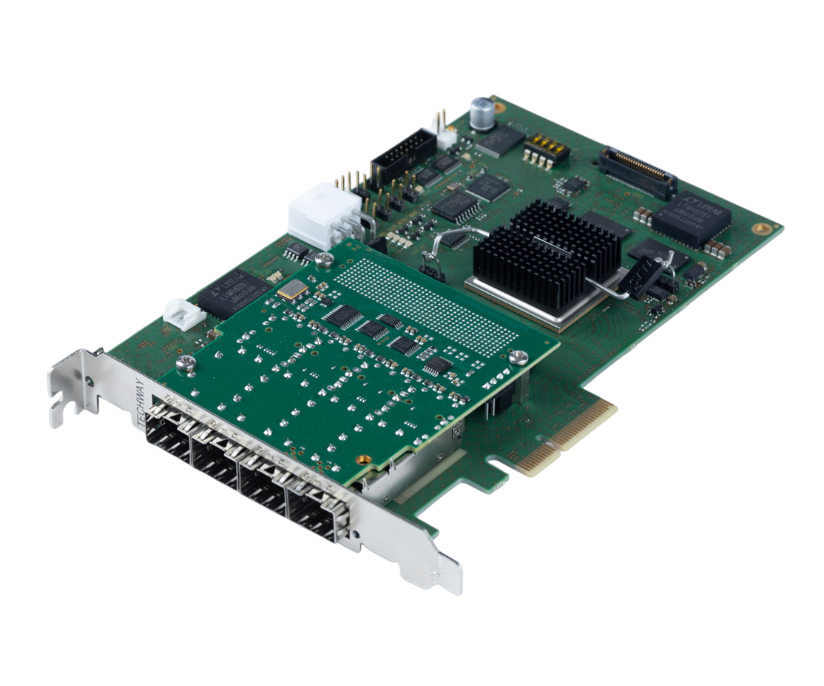

DAQ Cards (DAQ4)

DAQ cards provide the PCIe interface between the readout system and the data acquisition computer. The current commercial version, DAQ4, delivers a maximum throughput of 230 Mevents/s to computer. For demanding high-rate applications, the readout software can support up to two DAQ4 cards in a single computer, enabling a combined throughput of about 460 Mevents/s.

System Design Considerations

Applications with fewer than 1,024 channels can use a simplified configuration without a separate DAQ card or Clock & Trigger board. In this setup, the FEB/D board internally generates all necessary clock, synchronization, and test signals. Data transmission is handled by a Gigabit Ethernet mezzanine that interfaces directly to a standard GbE port on the acquisition computer, with maximum system throughput of 15 Mevents/s. This architecture forms the foundation of the PETsys Evaluation Kit, our ready-to-use development platform.

Whether your application requires a small or large channel count, selecting the optimal readout architecture depends on several key factors:

- Detector module design and scanner geometry

- Total channel count and per-channel counting rate

- Trigger filtering requirements and data acquisition rate

- Number of independent SiPM bias channels needed

- Required bias current capacity

PETsys provides comprehensive support throughout the design process, including architecture selection and full remote assistance during installation and commissioning.

Firmware and Software

FPGA Processing and Intelligent Triggering

Both FEB/D and DAQ boards utilize large FPGAs running proprietary firmware that manages critical data processing functions including data merging, event sorting, framing, and transmission.

FEB/D firmware also implements sophisticated energy and coincidence trigger algorithms:

- Events sharing the same timestamp (after time-walk correction) are automatically grouped

- Energy values are calibrated and summed within groups

- Groups exceeding configurable thresholds are flagged for transmission

- Trigger bits are forwarded to the Clock & Trigger board to generate PET coincidence triggers

This filtering significantly reduces data volume while preserving all critical coincidence events required for tomography.

Data Acquisition Software

PETsys provides open data acquisition software featuring:

- GUI-based system configuration for intuitive and easy operation

- Command-line tools with scripting support for automation, batch processing, and advanced workflows

- Integrated ASIC configuration and calibration tools, including register-level control, threshold setting and channel characterization and calibration.

- Comprehensive data flow management from acquisition to storage

- Optional real-time data processing for list-mode generation

- Flexible integration options to support custom and third-party applications